## Reporte de actividades

Guillermo Tejeda 19-05-2012

### **ACORDE**

- Mas pruebas con DAQ.

- Aun con problemas.

- Date -> nunca se presentaron esos problemas en el P2.

Todas las señales del Trigger responden bién.

Lunes hablar con Filippo para revisar comunicación con SIU.

### ITS

- Aux Card -> Esquemáticos terminados y revisados.

- Ruteo para grupo de Cagliari.

- Solo se trabajara en el diseño del Read Out del pixel.

- Diseñar todo desde las compuertas.

- Diseñar priority encoder -> sincrono y asincrono.

- Diseñar token ring -> sincrono y asincrono.

- Pruebas de diferentes arreglos de matrices.

- Verificar área y potencia

#### Luis

- Terminado programa de FPGA!

- Revisar comunicación USB

- Software de control

- Pruebas de comunicación

- Revisión de datos de simulación.

- Archivo de entrada -> ok

- Archivo de salida -> ok

- Formato -> ok

- Tiempos -> ok

- (Código y simulación se revisarán con software de aquí).

#### Cubo

- Cubo terminado (leds).

- -> Construcción de PCB.

- (Definir parte de potencia para las columnas)

- -> Firmware.

- -> Material completo.

### Material extra

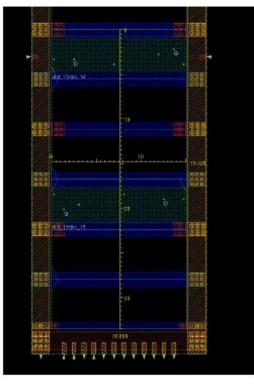

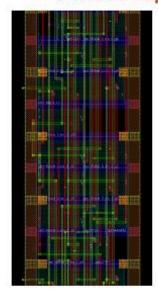

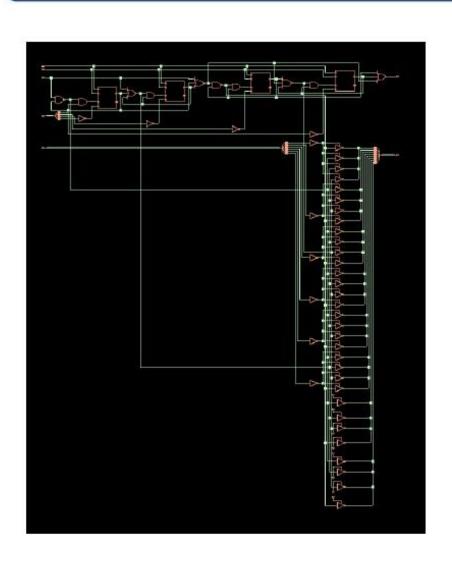

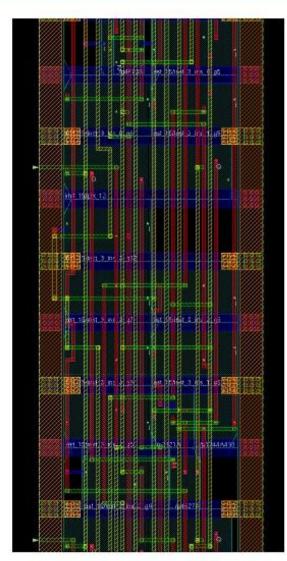

### Placement & route 256 pixels

Horizontal for 50μm 2 x Std Cell height 5.6μm FF width 15.68μm + Std Cell Area digital Pixel 558μm<sup>2</sup>

Vertical min. placement FF width 15.68 µm 3 x Std Cell height Area digital pixel 263µm<sup>2</sup>

TowerJazz 0.18um 1.8 V 6 Metal Layers

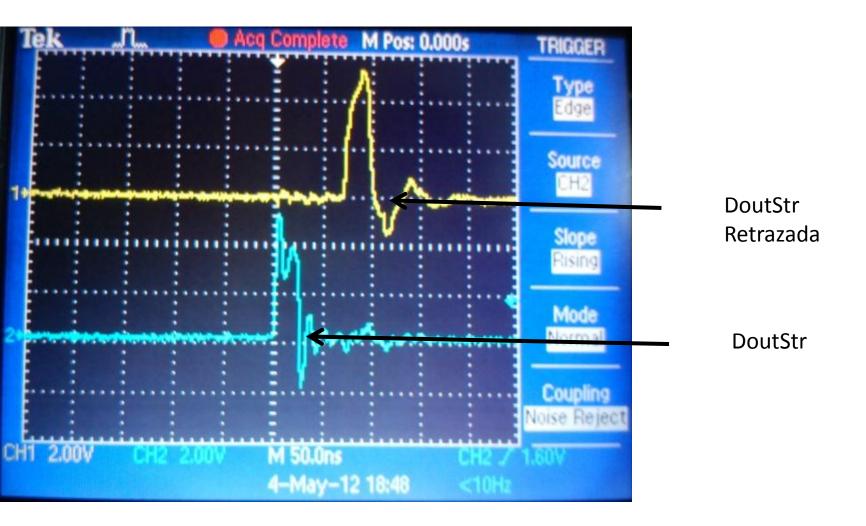

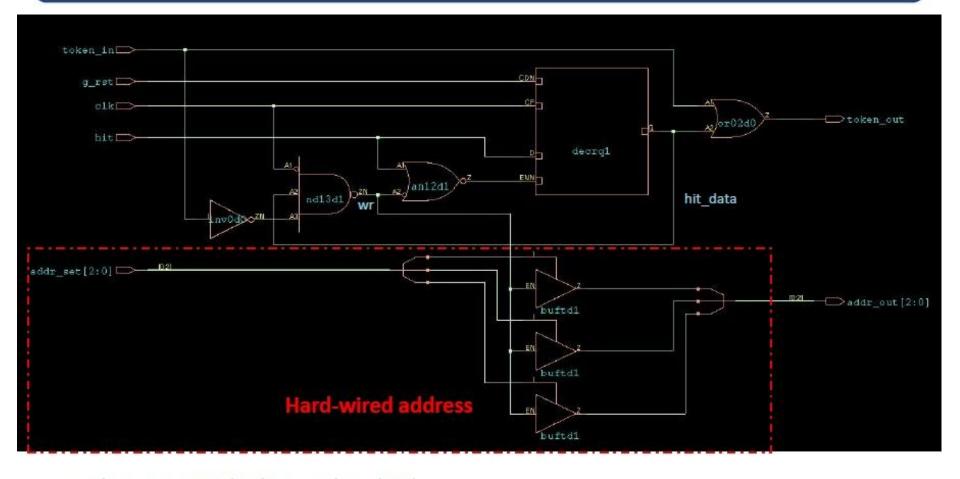

## Token ring pixel cell

```

token_out = OR( token_in, hit_data);

wr = AND (!clk, hit_data, !token_in );

The pixel is reset @posedge clk when hit =0 and wr =1

```

1 bit address =  $2.8 \times 5.6 \mu m^2$ 8 bit address =  $125 \mu m^2$

# Token ring 4x

1 pixel 15 x 30 μm<sup>2</sup> tot = 450 μm<sup>2</sup>