## Electronics plans

G. Tejeda Muñoz MuonID México Meeting December 15, 2022

- Transformative **discovery in science** is driven by **innovation in technology**. This mean that our boldest undertakinkgs in particle physics **have at their foundation** <u>precision</u> <u>instrumentation</u>.

- We are firmly conviced that to reveal the profound connections underlying everything we see from the smallest scales to largest distance of the universe, to understand its fundamental constituents, and **to reveal what is still unknow**, **we must invent**, **develop and deploy advanced instrumentation**.

## Introduction

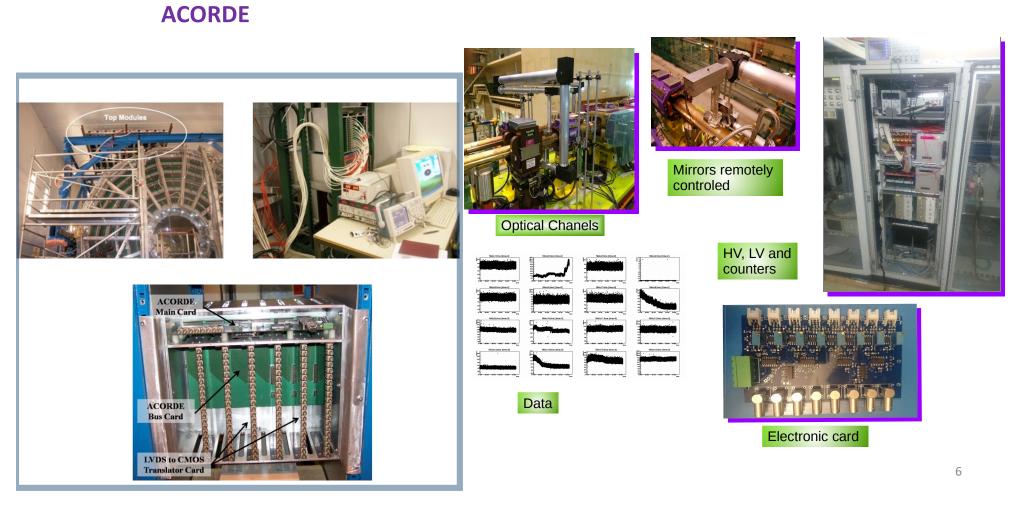

• ACORDE

• TPC

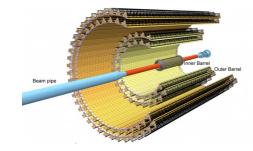

• ITS Upgrade

## • BELLE II (LABM)

FDD

CTP

#### Introduction (Associated Electronics to High Energy Experiment)

# Electronics in the detector

- FEE (depend on detector type)

- ReadOut

- DAQ system communication

- TRIGGER system communication

- Debugging communication

- Power Supply

- Cabling

- Cooling

- DCS interfce

LABM

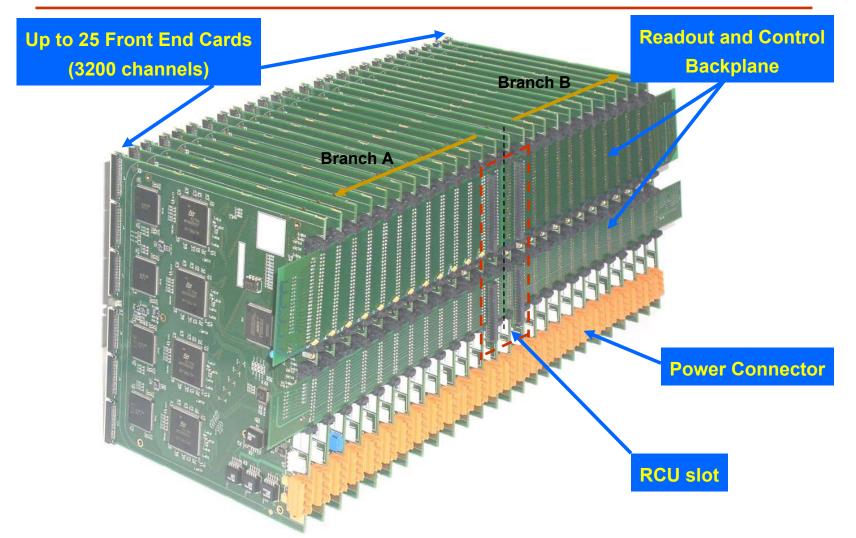

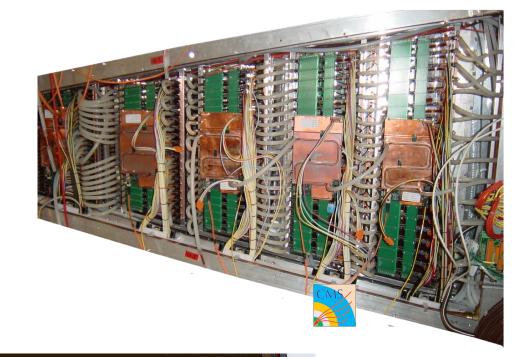

## **Readout Backplane – example of readout partition**

## RPC FEE

### First proto

2017 proof of principle for <u>CMS-MUON-TDR-016</u>

2 PetiROC2A + FPGA Cyclone II + ETHERNET directly on strip PCB (50 cm)

#### Feb V0 2018 First FEB (Conf. note) 1 PetiROC2A +

MEZZANINE with FPGA Cyclone II + ETHERNET

#### ote) Feb V1 2019 FEB without mezzanine 2 PetiROC2B

+ FPGA Cyclone V + ETHERNET

Feb V2 2021 Non-rad hard for iRPC Demo

6 PETIROC2C + 3 FPGA Cyclone V + Optical GBT

#### Feb V3 $\rightarrow$ 2023 Rad hard final

6 PETIROC2C + 3 FPGA PolarFire + Optical GBT

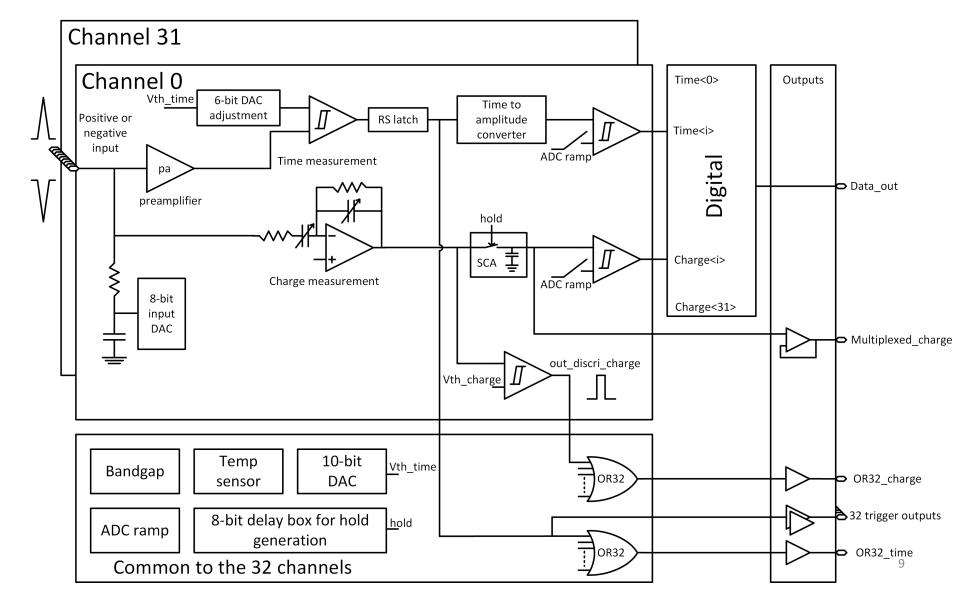

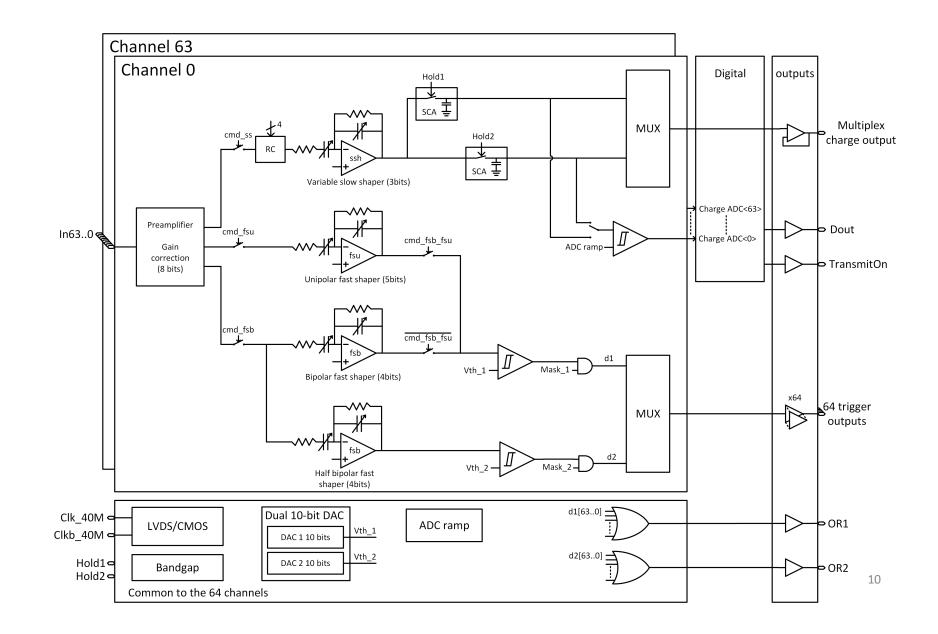

# Petiroc 2C (RPC)

## Channels distributions example

## • 13500 Channels

RPC:

422 PETIROC chips 104 FEE cards with 4 chips (128Ch/card) 13 CRU with 8 FEE connected PMT or SiPM:211 MAROC chips53 FEE cards with 4 chips (256 Ch/card)7 CRU with 8 FEE connected

Equivalent for PicoTDC.

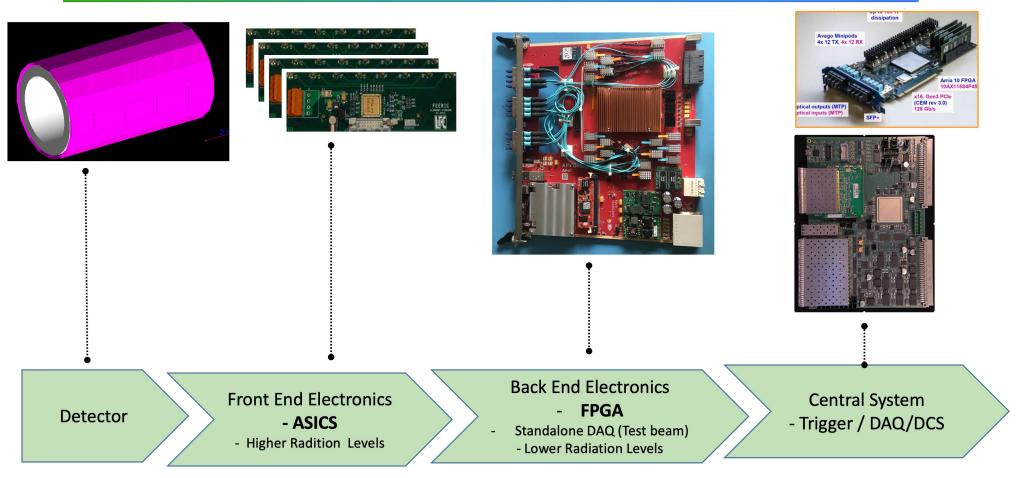

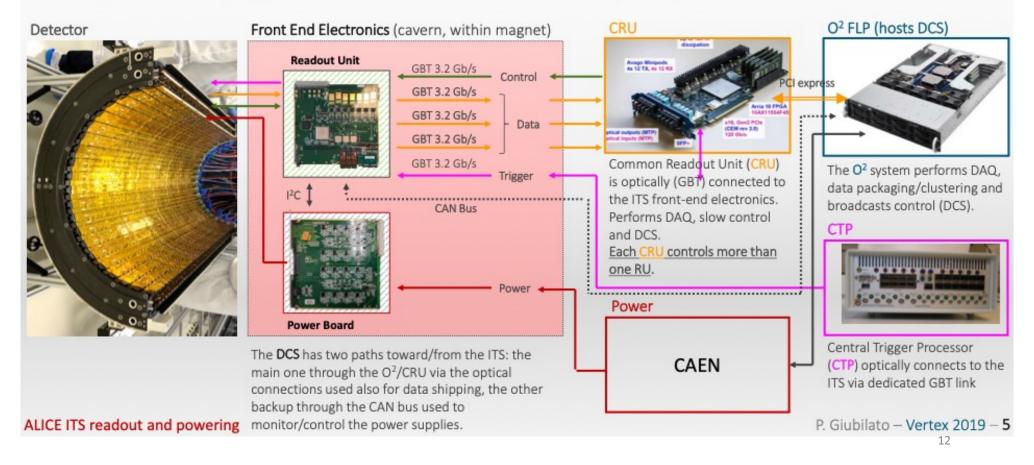

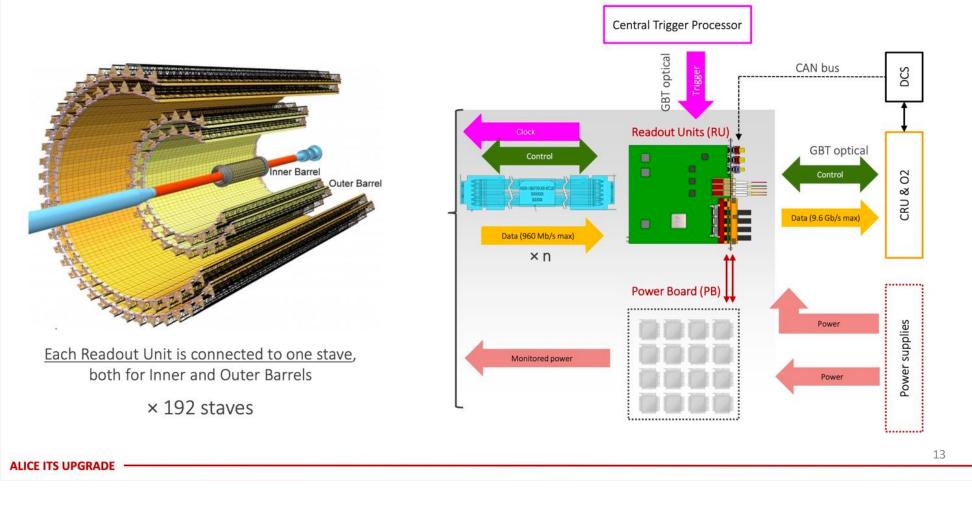

- The ITS Front End Electronic (FEE) is divided into modular Readout Units (RU), identical for each layer.

- Each readout unit controls an entire stave, including power to the sensors (through custom-made Power Boards).

- The experiment DAQ, Trigger and Control interfaces with the RU only through the Common Readout Unit.

## Specifications – ITS Readout Electronics is organized in Readout Units (RU)

The ITS front-end electronics are divided into **192** modular **Readout Units**, each connected to one ITS stave, and optically interfaced with both the Common Readout Unit (CRU) and the Central Trigger Processor (CTP).

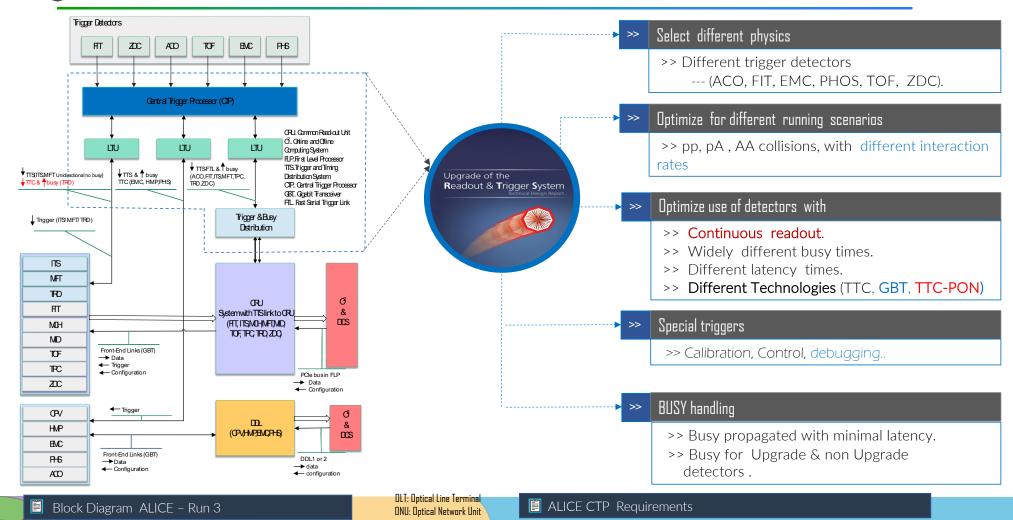

### CTP Requirements for LHC-Run3

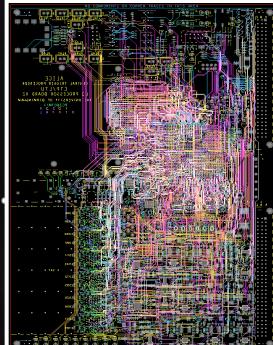

## ALICE Trigger board for LHC-Run3

- Kintex-Ultrascale FPGA

- Single universal trigger board (CTP/LTU board).

- Interface between CTP and LTUs is via TTC-PON and optical fan-out unit.

- Will still be based on a VME-type 6u board (VME for power only).

- PCB design

•

- \* 20 Layers (I-TERA MT40 material for highspeed digital multilayer)

- All clocks have the same length

- 2GB DDR4 Memory

- 2 Synthesizers

- 20 Optical Links (up to 11 Gbps)

#### Advance Processor board (CMS-Level 1 -- HL- LHC)

## APx- Family card for Phase 2 Trigger: Calorimeter, Correlator Muon.

Demonstrator for a multi-purpose, customizable, common processing platform, suitable for wide-scale use in CMS back-end trigger subsystems.

#### Virtex Ultrascale+ FPGA

- Flexible and expandible

- Control via ZYNQ SoC (ELM1 Embedded Linx Mezznine)

- Based on ATCA standard

- PCB design

\* 20 Layers (I-TERA MT40 material for high-speed digital multilayer)

- ~ 100 Rx/Tx Optical links (28 Gbps)

- 4 Synthesizers

- 2 Retimers Chips

- 10GbE ELM connection supported via SFP

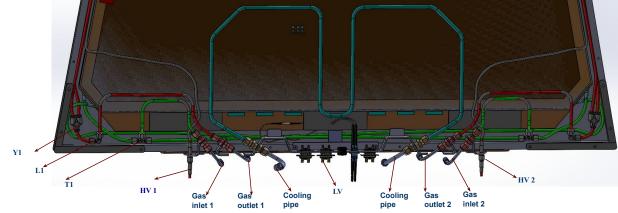

## cooling

RPC gas and cooling

## Electronic system tasks

- Design of the FEE for RPCs, PMTs or SiPM.

- Design of the Read Out Unit for the FEE.

- Design of the DCS and electronics communications.

- Design of the trigger and control modules.

- Design of the DAQ system communication.

## Experience in electronics

- Dr. Luis Alberto Perez Moreno

- Guillermo Tejeda Muñoz

- David Regules Medel

- Yael Antonio Vasquez Beltran

- Emigdio Jimenez Dominguez

- Omar Mancilla Martinez

Thank You