# Gamma Air Watch (GAW): the electronics and trigger concept

AD5318 octal out

DAC

P. ASSIS<sup>1</sup>, G. AGNETTA<sup>2</sup>, P. BROGUEIRA<sup>1</sup>, O. CATALANO<sup>2</sup>, G. CUSUMANO<sup>2</sup>, N. GALLÌ<sup>2</sup>, S. GIARRUSSO<sup>2</sup>, G. LA ROSA<sup>2</sup>, M. PIMENTA<sup>1</sup>, G. PIRES<sup>1</sup>, F. RUSSO<sup>2</sup>, B. SACCO<sup>2</sup>

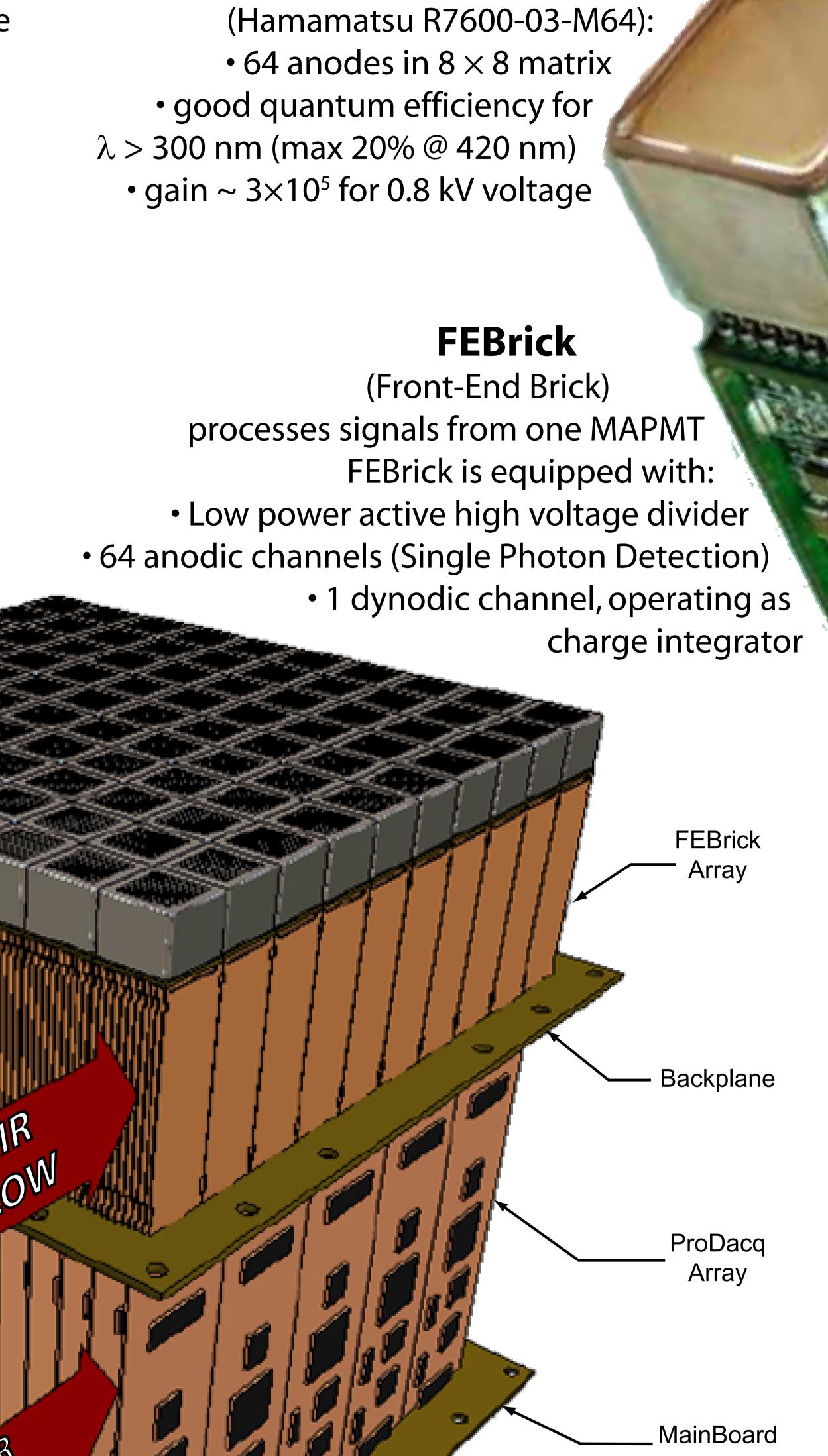

**MAPMT**

The new approach of GAW for the detection of gamma rays imposes specific requirements on the electronics design.

#### **Electronics main characteristics:**

- $\sim 10^5$  pixels

- Single Photon Counting

- free running data-taking

- 100 MHz acquisition rate

- trigger based on the number of active pixels

#### **Focal Surface Detector:**

- array of MAPMTs

- Modular Front-End electronics (FEBrick)

- Backplane

- Modular DAQ (ProDacq)

AIR

Front-END

**Power Board**

(HV & LV)

All FEBrick units are

placed together on the top of a backplane. ProDacq units are placed on the bottom. Backplane is in charge of connecting FEBrick units signals to the relevant ProDAcq units.

on a mainboard equipped with Trigger and Timing Synchronization devices, instrumentation management, power supply and external host interface.

ProDAcq units are terminated

Management

**Board**

### Trigger system

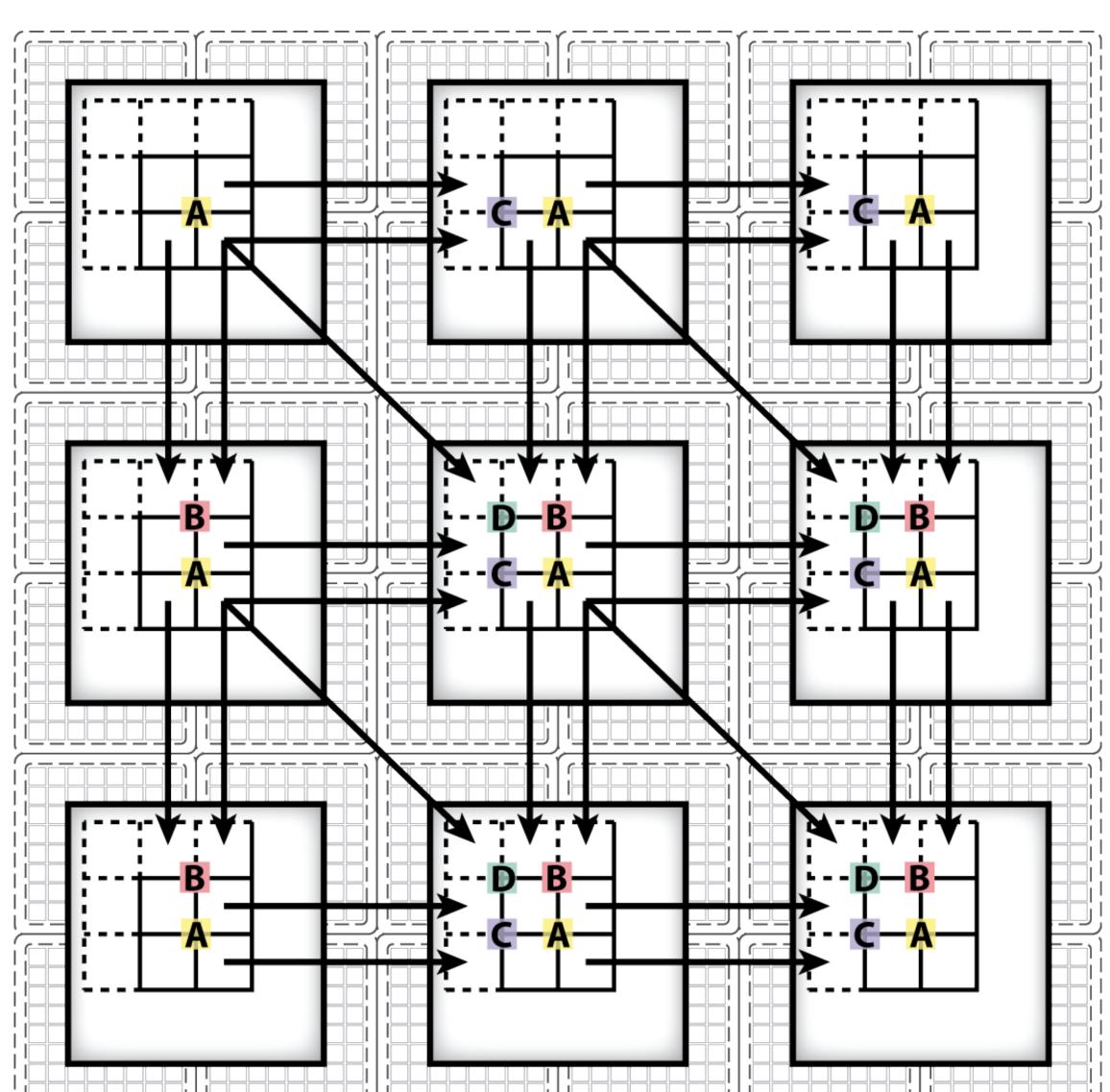

based on three trigger levels:

1<sup>st</sup>: fast discriminator on FEBrick = simple threshold on each pixel signal -> transformed in digital signals (Pixel-on)

2<sup>nd</sup>: the focal surface is searched, online, by FPGAs on the MainBoard for a given number of pixel-on inside all possible squares of  $2 \times 2$  PMTs.

3<sup>rd</sup>: validation of second level triggers. Decide the relevant

Each Mainboard FPGA receives data from one FEBrick. Each FPGA exchanges data with its neighbours. The trigger operates in a pipelined scheme and makes a decision each 10ns.

Relevant data is then read from the internal memories

## **ProDAcq**

(Programmable Data Acquisition)

- Managed by a reprogrammable FPGA

- Digital signals recorded in memory

- Input analogue signal sampled by ADCs

- Each ProDacq receives data from one **FEBrick**

\*\*\*\*\*\*\*